понедельник, 28 декабря 2020 г.

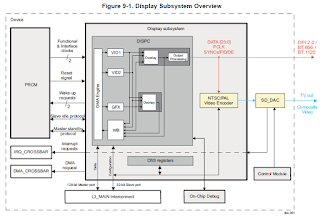

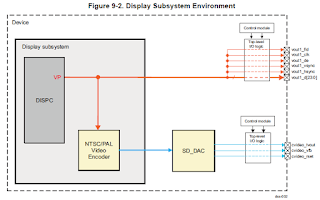

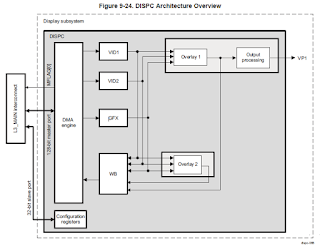

ti dss (display subsystem) (tda3x)

четверг, 24 декабря 2020 г.

Как войти в BIOS на ноуте sony vaio

вторник, 22 декабря 2020 г.

Установка 7zip на fedora/ubuntu

1. Ubuntu:

sudo apt install p7zip-full p7zip-rarОснованные на Debian дистрибутивы идут с тремя связанными с 7zip пакетами:

- p7zip: включает 7zr (минимальный инструмент архивирования 7zip), который может работать только с родным форматом 7z.

- p7zip-full: содержит 7z, который может поддерживать 7z, LZMA2, XZ, ZIP, CAB, GZIP, BZIP2, ARJ, TAR, CPIO, RPM, ISO и DEB.

- p7zip-rar: содержит плагин для извлечения файлов RAR

Дистрибутивы, основанные на Red Hat, предлагают два связанных с 7zip пакета:

- p7zip: содержит команду 7za, котомая может поддерживать 7z, ZIP, GZIP, CAB, ARJ, BZIP2, TAR, CPIO, RPM и DEB.

- p7zip-plugins: содержит команду 7z и дополнительный плагин для расширения возможностей команды 7za (например, извлечение ISO)

четверг, 17 декабря 2020 г.

среда, 16 декабря 2020 г.

Регулировка реле давления

1) Как регулировать реле давления на насосной станции https://www.youtube.com/watch?v=SBjzXLkebl4&ab_channel=Tehlab

вторник, 15 декабря 2020 г.

понедельник, 14 декабря 2020 г.

Багажник или рейлинги на субару импреза III (2008 г.в.)

суббота, 12 декабря 2020 г.

Ремонт батареи ноута, замена аккумов 18650 (asus, lenovo)

1) Как восстановить аккумулятор ноутбука, пример ремонта - Часть 1

воскресенье, 6 декабря 2020 г.

Кокосовое печенье

1) КАК ОТКРЫТЬ КОКОС и собрать КОКОСОВОЕ МОЛОЧКО

Доступ в BIOS в ноуте lenovo ideapad s400

суббота, 5 декабря 2020 г.

Разборка ноута asus eee pc 1201n

1) Asus Eee PC 1201 - Разборка. Чистка https://www.youtube.com/watch?v=T65V0z5rTRg&ab_channel=INERTICOService

2) Ноутбук Asus Eee PC 1201 PN. Разборка ноутбука. Замена термопасты и чистка ноутбука https://www.youtube.com/watch?v=zZcM-mTcQCQ&ab_channel=%D0%A2%D0%B5%D1%85%D0%BD%D0%BE

3) Как разобрать ASUS EEE 1201N / How to disassemble NetBook ASUS EEE 1201N https://www.youtube.com/watch?v=ZafoFkeIa-8&ab_channel=IVARBU

среда, 2 декабря 2020 г.

Магический квадрат

1) Магический квадрат

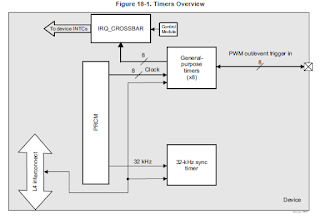

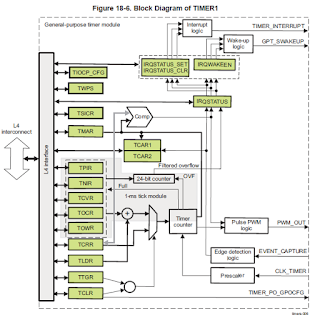

tda3x timer

The device includes several types of timers used by the system software, including eight general-purpose (GP) timers, and a 32-kHz synchronized timer (COUNTER_32K). Figure 18-1 shows a high-level block diagram of the device timers.

пятница, 27 ноября 2020 г.

вторник, 24 ноября 2020 г.

Компьютерное зрение (теория)

вторник, 17 ноября 2020 г.

понедельник, 2 ноября 2020 г.

cortex m4

1) Specifications https://developer.arm.com/ip-products/processors/cortex-m/cortex-m4

вторник, 27 октября 2020 г.

global/rolling shutter и экспозиция

1) Global shutter vs Rolling shutter: подробный разбор https://cctvlens.ru/publications/global-shutter-vs-rolling-shutter-podrobnyj-razbor/

четверг, 8 октября 2020 г.

четверг, 1 октября 2020 г.

bbb, rpi i2c driver on linux

1) Пишем модуль ядра Linux: I2C https://habr.com/ru/post/413249/

вторник, 29 сентября 2020 г.

Популярная электроника

понедельник, 28 сентября 2020 г.

среда, 23 сентября 2020 г.

ti memory management units (MMUs)

• Preventing an initiator from making accesses to unmapped pages of the system memory

понедельник, 21 сентября 2020 г.

fpga (cpld) memory mapped register

1) Altera + OpenCL: программируем под FPGA без знания VHDL/Verilog https://habr.com/ru/post/269009/

суббота, 19 сентября 2020 г.

пятница, 18 сентября 2020 г.

понедельник, 14 сентября 2020 г.

Курсы для детей по scratch, gamemaker

1) scratch https://kodium.online

2) gamemaker http://kodini.ru/courses/gamemaker#courses-nav

3) minecraft (ComputerCraftEdu) https://foxford.ru/courses/2723/landing

1) Как установить Minecraft, мод ComputerCraftEdu и Scratch https://academiaguru.ru/kak-ustanovit-minecraft-i-mod-computercraftedu/

2) ComputerCraftEdu [1.8.9] [1.7.10] https://www.geroncraft.ru/computercraftedu/

esp32, esp8266 with wifi

1) https://ru.m.wikipedia.org/wiki/ESP32

2) ESP32: знакомимся, пишем и запускаем первую прошивку https://m.habr.com/ru/post/309746/

3) Микроконтроллер ESP32 и проекты Arduino https://arduinomaster.ru/platy-arduino/esp32-arduino-raspinovka-arduino-ide/

пятница, 11 сентября 2020 г.

Замена трещотки на заднем колесе велика

1) КАК починить трещотку велосипеда, обслуживание https://www.youtube.com/watch?v=xs4nCTMVSjw&ab_channel=FisherMan

2) Как снять трещотку

3) Ремонт трещотки https://www.youtube.com/watch?v=kmfyxYQdGdk&ab_channel=serjiolife

4) Пром подшипник на дешевую втулку под трещотку

понедельник, 7 сентября 2020 г.

ti tda3 memory mapping (inner nor-, nand-, sram-memories and external sdram ddr), memory subsystem (emif, gpmc, ocm) and interconnect (L3, L4)

GPMC, EMIF, OCM in L3, L4 interconnect

EMIF controller

Ремонт бачка унитаза

Ссылки:

1) Так делать надо только в том случае, если вы собирались переставлять бак, потому что никак кроме отсоединения бака, закручивания нижней части слива и присоединения бака опять восстановить работоспособность сливной системы не удастся https://youtu.be/Qv7yqWJ-kQU

среда, 2 сентября 2020 г.

Устройство автомобиля (ДВС и электродвигатель)

Вики:

1) Кривошипно-шатунный механизм

2) Двигатель внутреннего сгорания

3) Электрический двигатель

4) Поршень

ДВС -> электродвигатель:

1) https://meduza.io/cards/kak-prevratit-mashinu-v-elektrokar

2) https://www.kolesa.ru/article/elektromobil-svoimi-rukami-kak-zachem-i-skolko-eto-stoit

Оппозитный двигатель и v-образный двигатель:

1) Оппозитный двигатель

2) v-образный двигатель

Стандарты аналогового и цифрового телевидения

Ссылки:

1) https://ru.wikipedia.org/wiki/PAL

2) https://ru.wikipedia.org/wiki/NTSC

3) Автоматическая регулировка усиления

4) Цифровое телевидение

5) Несущий сигнал

6) Видеосигнал

7) Спектр

8) Прогрессивная развертка

9) Чересстрочная развертка

1) Дисперсия света

вторник, 1 сентября 2020 г.

четверг, 27 августа 2020 г.

connect old phone lcd to arduino, rpi or stm32

1. phone lcd

1) Подключаем дисплей от сотика или мобильного телефона к Ардуино https://www.youtube.com/watch?v=ShnyOOcfbhc